超高频读写器的RFID系统构成与硬件结构

来源:

安的电子 日期:2022-07-15

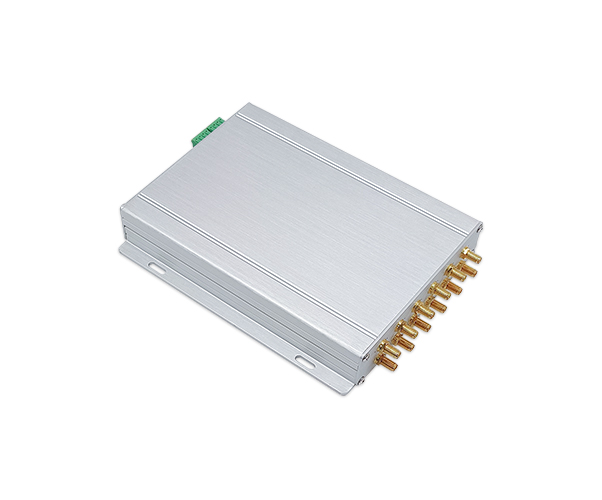

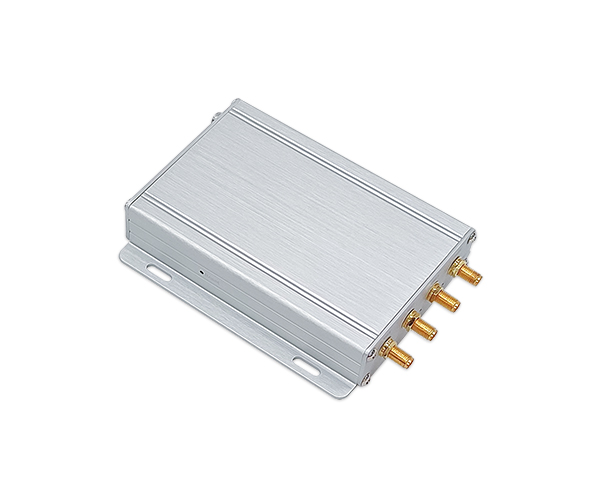

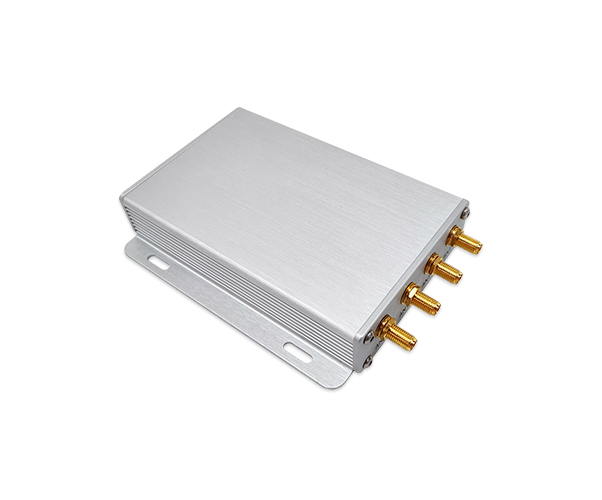

读写器的工作频率为915 MHz,是基于无源反射调制技术和模块化设计原理的 RFID读写器,工作距离长达 10 m。

1.RFID系统构成

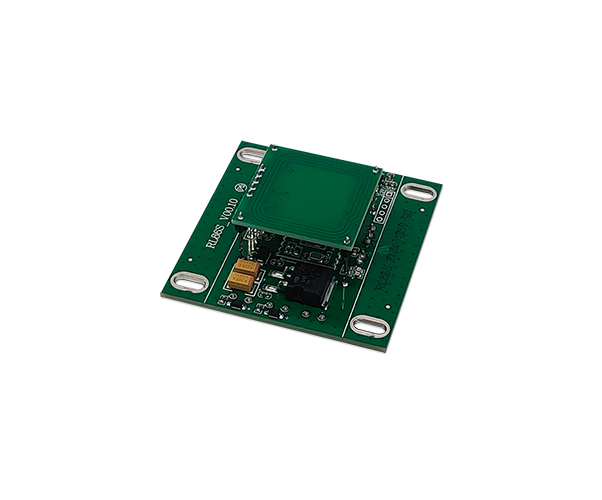

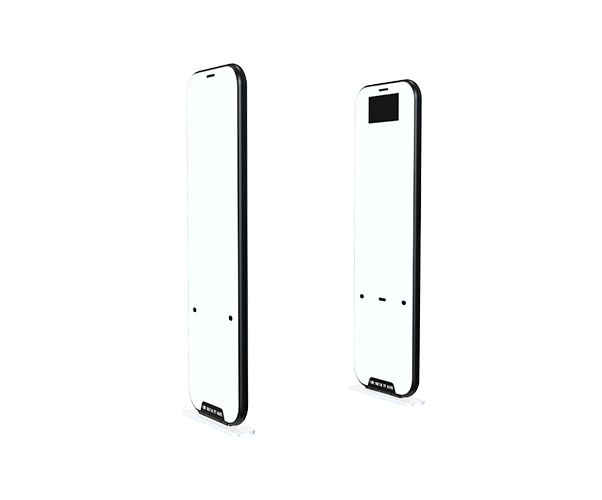

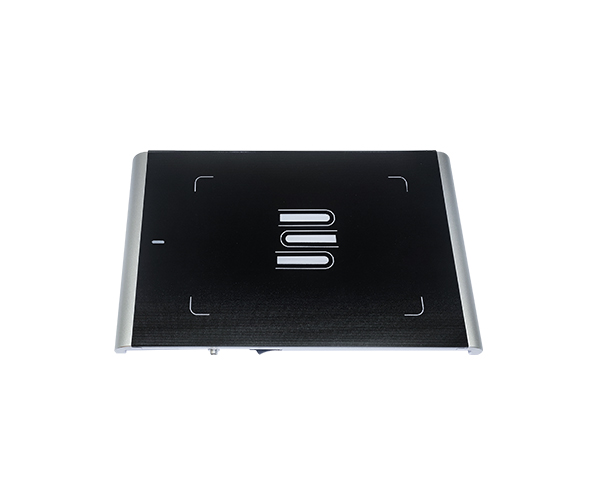

UHF频段RFID系统是无源RFID系统,由读写器和电子标签组成,如图8.23所示。当电子标签进入读写器的能量场,电子标签的能量检测电路将射频信号转化为直流信号,供其工作。同时,芯片内部的数据解调部分从接收到的射频信号中解调出数据并送到控制逻辑。控制逻辑负责分析数据并执行相应操作,包括从EEPROM读数据或写入数据,将数据调制发送出去。

2.读写器的硬件结构

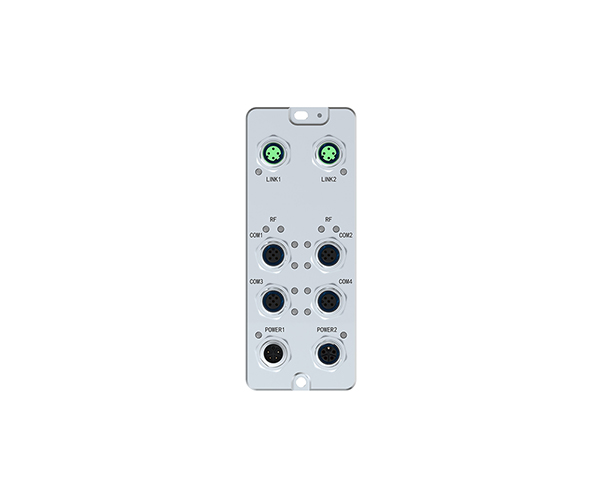

915 MHz的读写器主要由天线、射频模块和主控模块3部分组成。射频模块由发送部分和接收部分构成,发送部分产生射频信号及射频能量,给无源电子标签提供能量;接收部分对由天线接收的反射调制信号进行解调、放大及滤波。主控模块控制与电子标签的通信过程;主机应用软件进行通信,并执行应用软件发来的命令。

射频识别系统采用时分复用的工作方式,读写器输出命令信号与接收电子标签反射调制信号是在不同的时间段进行的。

(1)数字锁相环技术

在射频部分,采用晶体振荡器和压控振荡器以全数字锁相环的形式产生 915 MHz射频信号。传统的锁相环由模拟电路实现,而全数字锁相环与传统的模拟电路的实现方法相比,具有精度高且不受温度和电压影响、环路带宽和中心频率编程可调、易于构建高阶锁相环等优点,并且应用在数字系统中时不需A/D及D/A转换。

(2)信号接收

天线接收的反射调制信号经过定向耦合器到接收通路,检波后的信号通过差动放大、低通滤波器和运算放大后,进行A/D转换再送至主控模块进行解码。

读写器进行读写操作时,读写器与电子标签的距离不是固定不变的。如果读写器与电子标签距离近,读写器接收到的反射调制信号较强;如果读写器与电子标签距离远,读写器接收到的反射调制信号就较弱。为了在读写器的工作距离内得到稳定可靠的接收数据,需要对A/D转换之前的运算放大器进行放大倍数控制,较弱的接收信号需要较大的放大倍数。

为了保持接收信号的稳定,采用了移动终端功率控制方案:反射信号变强,降低接收通路的放大倍数;反之,反射信号变弱,提高其放大倍数。采用对数放大器对反射调制信号进行电平检测,然后输入到主控模块进行算法分析,输出控制信号改变末级运算放大器的反馈电阻大小,即可实现运算放大器的放大倍数的自动控制,进而实现A/D转换前信号幅度的稳定。

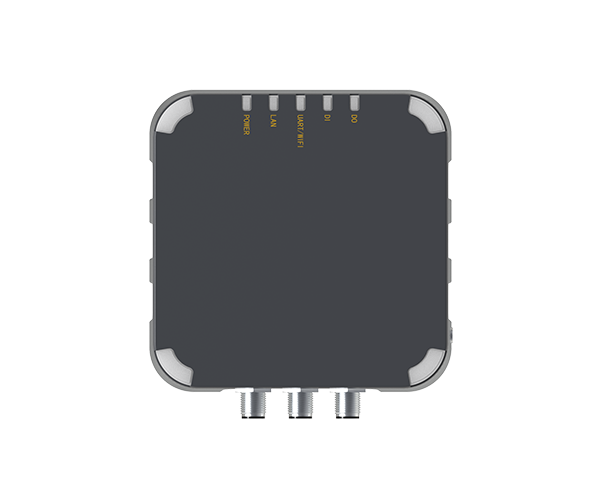

(3)主控模块

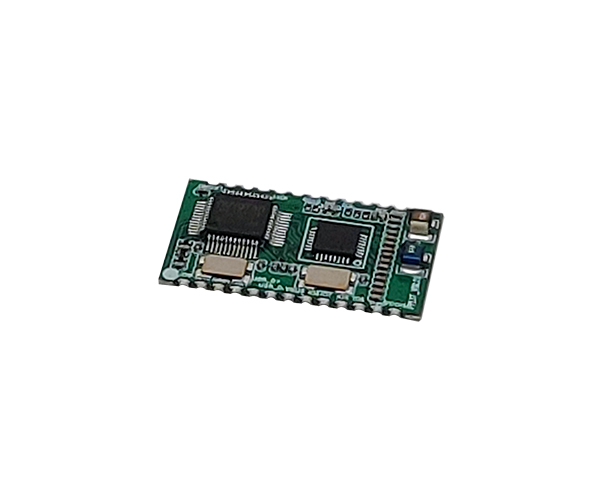

主控模块的核心处理器为数字信号处理器(Digital Signal Processing,DSP),该 DSP 芯片运算速度为 50 MIPS(MIPS:每秒执行百万条指令),片内有 10 KB 双向访问 RAM,支持64 KByte 的数据空间和 64 KByte 的程序空间,能够满足射频识别系统的要求。主控模块的硬件框图如图 8.24 所示,本系统采用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)完成整个系统的逻辑电路设计。

实际系统中,扩展了64 KByte 的 SRAM,但因DSP 最多支持外部扩展 64 KByte的数据空间,因此,模拟CE控制信号由DSP通过CPLD中的逻辑电路来控制,从而决定选择SRAM的高地址段 64 KByte 的存储空间还是低地址字段的存储空间。这样,在符合 DSP 的外扩数据空间要求的基础上又增加了宝贵的存储资源。除了 SRAM,还配置了64 KByte 的 Flash,以满足DSP引导装入程序的需要。

(文章来源于网络,如有侵权请联系删除。)

1.RFID系统构成

UHF频段RFID系统是无源RFID系统,由读写器和电子标签组成,如图8.23所示。当电子标签进入读写器的能量场,电子标签的能量检测电路将射频信号转化为直流信号,供其工作。同时,芯片内部的数据解调部分从接收到的射频信号中解调出数据并送到控制逻辑。控制逻辑负责分析数据并执行相应操作,包括从EEPROM读数据或写入数据,将数据调制发送出去。

2.读写器的硬件结构

915 MHz的读写器主要由天线、射频模块和主控模块3部分组成。射频模块由发送部分和接收部分构成,发送部分产生射频信号及射频能量,给无源电子标签提供能量;接收部分对由天线接收的反射调制信号进行解调、放大及滤波。主控模块控制与电子标签的通信过程;主机应用软件进行通信,并执行应用软件发来的命令。

射频识别系统采用时分复用的工作方式,读写器输出命令信号与接收电子标签反射调制信号是在不同的时间段进行的。

(1)数字锁相环技术

在射频部分,采用晶体振荡器和压控振荡器以全数字锁相环的形式产生 915 MHz射频信号。传统的锁相环由模拟电路实现,而全数字锁相环与传统的模拟电路的实现方法相比,具有精度高且不受温度和电压影响、环路带宽和中心频率编程可调、易于构建高阶锁相环等优点,并且应用在数字系统中时不需A/D及D/A转换。

(2)信号接收

天线接收的反射调制信号经过定向耦合器到接收通路,检波后的信号通过差动放大、低通滤波器和运算放大后,进行A/D转换再送至主控模块进行解码。

读写器进行读写操作时,读写器与电子标签的距离不是固定不变的。如果读写器与电子标签距离近,读写器接收到的反射调制信号较强;如果读写器与电子标签距离远,读写器接收到的反射调制信号就较弱。为了在读写器的工作距离内得到稳定可靠的接收数据,需要对A/D转换之前的运算放大器进行放大倍数控制,较弱的接收信号需要较大的放大倍数。

为了保持接收信号的稳定,采用了移动终端功率控制方案:反射信号变强,降低接收通路的放大倍数;反之,反射信号变弱,提高其放大倍数。采用对数放大器对反射调制信号进行电平检测,然后输入到主控模块进行算法分析,输出控制信号改变末级运算放大器的反馈电阻大小,即可实现运算放大器的放大倍数的自动控制,进而实现A/D转换前信号幅度的稳定。

(3)主控模块

主控模块的核心处理器为数字信号处理器(Digital Signal Processing,DSP),该 DSP 芯片运算速度为 50 MIPS(MIPS:每秒执行百万条指令),片内有 10 KB 双向访问 RAM,支持64 KByte 的数据空间和 64 KByte 的程序空间,能够满足射频识别系统的要求。主控模块的硬件框图如图 8.24 所示,本系统采用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)完成整个系统的逻辑电路设计。

实际系统中,扩展了64 KByte 的 SRAM,但因DSP 最多支持外部扩展 64 KByte的数据空间,因此,模拟CE控制信号由DSP通过CPLD中的逻辑电路来控制,从而决定选择SRAM的高地址段 64 KByte 的存储空间还是低地址字段的存储空间。这样,在符合 DSP 的外扩数据空间要求的基础上又增加了宝贵的存储资源。除了 SRAM,还配置了64 KByte 的 Flash,以满足DSP引导装入程序的需要。

(文章来源于网络,如有侵权请联系删除。)

智慧图书馆

智慧图书馆

智能制造

智能制造

RFID档案管理

RFID档案管理

RFID新零售

RFID新零售

智慧医疗

智慧医疗

会议签到

会议签到

高频RFID

高频RFID

超高频RFID

超高频RFID

RFID手持终端

RFID手持终端